## Pioneer

# Service Manual

SERVICE GUIDE ORDER NO. RRV2055

COMPACT DISC RECORDER

# PDR-555RW PDR-V500 PDR-19RW PDR-509

## PDR-555RW, PDR-V500, PDR-19RW, PDR-509

## **CONTENTS**

| 1. | BLOCK DIAGRAM                                             | 4  | 1 |

|----|-----------------------------------------------------------|----|---|

|    | 1.1 PDR-555RW, PDR-V500 AND PDR-19RW                      | 4  | 1 |

|    | 1.2 PDR-509                                               | 6  | 3 |

|    |                                                           |    |   |

| 2. | PRODUCT DESCRIPTIONS                                      | 8  | 3 |

|    |                                                           |    |   |

| 3. | PORT TABLE OF MICROCOMPUTER                               | 9  | ) |

|    | 3.1 MODE CONTROL OF PDR-555RW, PDR-V500 AND PDR-19RW      | ç  | ) |

|    | 3.2 MECHANISM CONTROL OF PDR-555RW, PDR-V500 AND PDR-19RW |    |   |

|    | 3.3 MODE CONTROL OF PDR-509                               |    |   |

|    | 3.4 MECHANISM CONTROL OF PDR-509                          |    |   |

|    |                                                           |    |   |

| 4. | PIN FUNCTION OF PRINCIPAL IC                              | 19 | ) |

|    | 4.1 AD1893JST                                             | 19 | ) |

|    | 4.2 BR93LC46AF                                            |    |   |

|    | 4.3 LC89585                                               | 20 | ) |

|    | 4.4 LH64256CK-70                                          | 22 | 2 |

|    | 4.5 PA9004A                                               |    |   |

|    | 4.6 PDJ014A                                               | 23 | 3 |

|    | 4.7 PDK033A or PDK041A                                    | 24 | 1 |

|    | 4.8 AK5340-VS                                             | 25 | 5 |

|    | 4.9 PD0236AD                                              | 26 | 3 |

|    | 4.10 PCM1800-1                                            | 26 | 3 |

|    |                                                           |    |   |

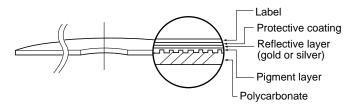

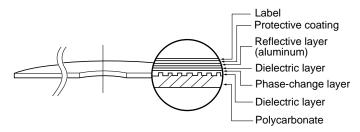

| 5. | RECORDING MECHANISM FOR CD-Rs AND CD-RWs                  |    |   |

|    | 5.1 DISC                                                  |    |   |

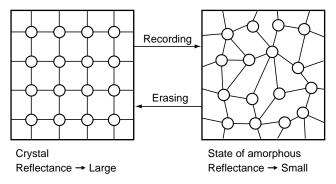

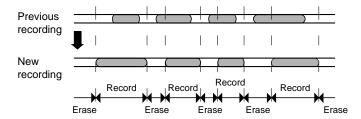

|    | 5.2 OVERWRITE RECORDING OF CD-RW                          | 27 | 7 |

| _  | DIGITIE (I/DO 0004)                                       |    |   |

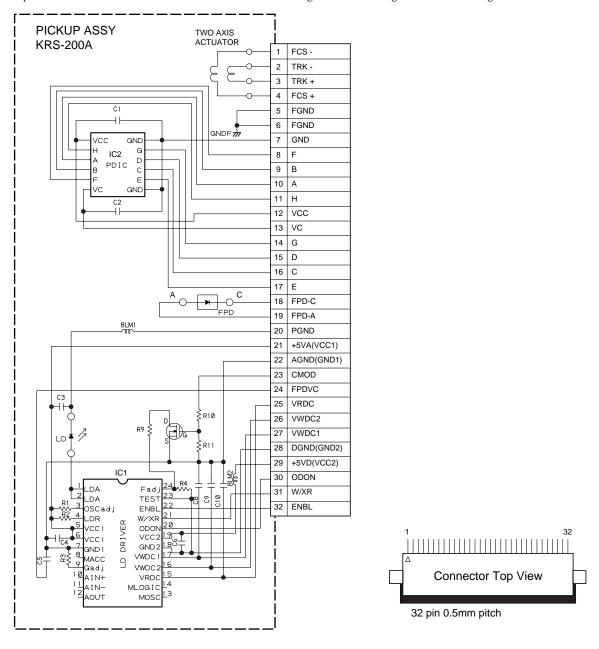

| 6. | PICKUP (KRS-200A)                                         | 28 | 3 |

| 7  | CIRCUIT DESCRIPTIONS                                      | 00 |   |

| ١. |                                                           |    |   |

|    | 7.1 SERVO CIRCUITS                                        |    |   |

|    | 7.1.2 Error Signal Generation Circuit                     |    |   |

|    | 7.1.3 Focus Servo                                         |    |   |

|    | 7.1.3 Focus Servo                                         |    |   |

|    | 7.1.5 Spindle Servo                                       |    |   |

|    | 7.1.3 Spiritile Servo                                     |    |   |

|    | 7.3 EFM-DIGITAL PLL                                       |    |   |

|    | 7.4 RF DETECTION                                          |    |   |

|    | 7.5 MIRROR CIRCUIT                                        |    |   |

|    | 7.6 AUDIO CIRCUITS                                        |    |   |

|    | 7.6.1 Analog Audio Input                                  |    |   |

|    | 7.6.2 A/D Converter                                       |    |   |

|    | 7.6.3 Hi-bit IC (PDR-19RW Only)                           |    |   |

|    | 7.6.4 D/A Converter                                       |    |   |

|    | 7.6.5 Analog Audio Output Block                           |    |   |

|    | 7.7 DIGITAL CIRCUITS                                      |    |   |

|    | 7.7.1 Digital Audio Interface Input Block                 |    |   |

|    | 7.7.2 Sampling Rate Converter                             | 31 | ı |

|    | 7.7.3 Clock-jitter Suppressor Circuit (PDR-509 Only)      | 31 | ı |

|    | 7.7.4 Data Selector                                       |    |   |

|    | 7.7.5 Digital Fader, Level Meter, Mute Blocks             |    |   |

|    | 7.7.6 Memory Control                                      |    |   |

|    | 7.7.7 EFM Encoding                                        |    |   |

|    | 7.7.8 Strategy Control                                    |    |   |

|    | 7.7.9 Digital Audio Interface Modulation                  | 32 | ) |

| 8. DETAILED DESCRIPTIONS OF OUTPUT TERMINAL CONTROL  8.1 DGAI (microcomputer,pin 48)and D8CM (microcomputer,pin 53)TERMINAL CONT  8.2 AGCON (ATIP decoder, pin 52) TERMINAL CONTROL  8.3 XCD (ATIP decoder, pin 69) TERMINAL CONTROL  8.4 GAINUP1 (ATIP decoder, pin 45) RW/XR (ATIP decoder, pin 66) TERMINAL CON  8.5 CDROPC (ATIP decoder, pin 46) TERMINAL CONTROL  8.6 GAINUP3 (ATIP decoder, pin 47) TERMINAL CONTROL  8.7 PHYERS (ATIP decoder, pin 52) TERMINAL CONTROL  8.8 SSEL (ATIP decoder, pin 51) TERMINAL CONTROL  8.9 ENBL (ATIP decoder, pin 70) TERMINAL CONTROL                                                                                                                                                                                                                                                                                                                                                                                       | TROL 32<br>                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

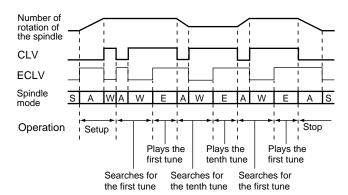

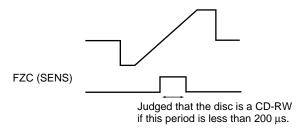

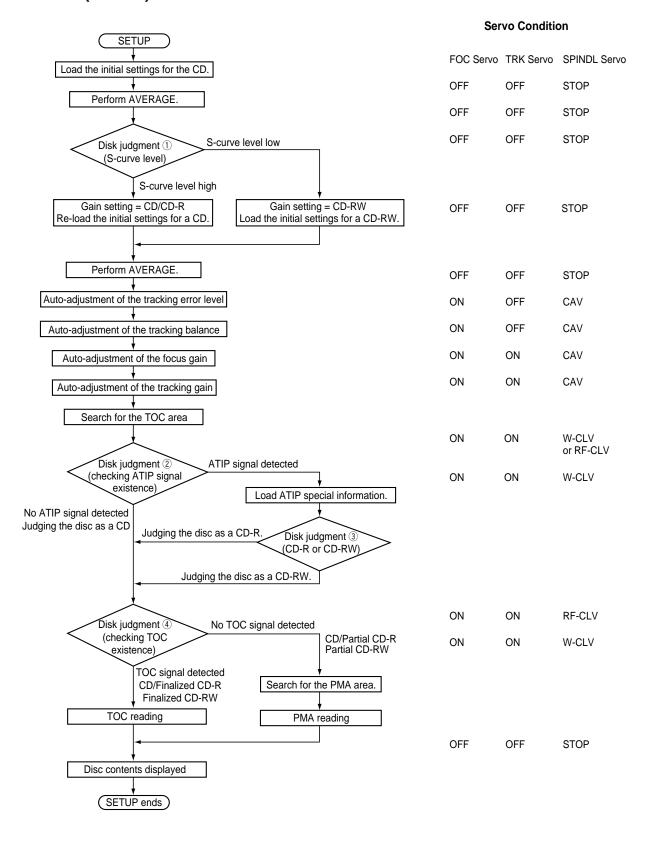

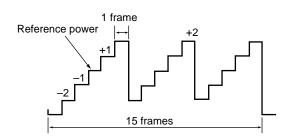

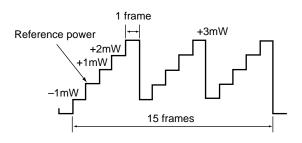

| 9. OPERATION DESCRIPTIONS 9.1 ABOUT POWER ON/OFF 9.1.1 Power-up (When the power outlet is active) 9.1.2 Power Down (When the power outlet is not active or power failure occurs) 9.2 ABOUT SERVO CONTROL 9.2.1 Seek Track 0 9.2.2 Focus ON 9.2.3 One-Track Jump (Direct Sequence) 9.2.4 One-Track Jump (Auto Sequence) 9.2.5 Ten-Track Jump 9.2.6 2N-Track Jump 9.2.7 M-Track Move 9.2.8 Fine Search 9.2.9 Loading Control 9.2.10 Spindle Control 9.3 ERASING (CD-RW ONLY) 9.3.1 Last-Track-Erase Operation 9.3.2 All-Track-Erase Operation 9.3.3 TOC-Erase Operation 9.3.4 ALL-Disc-Erase Operation 9.3.5 PCA-Erase Operation 9.3.6 PCA-Erase Operation 9.5.1 Tentative Judgment Using FZC (Distinguishing Between CD/CD-R and CD-R 9.5.2 Disc Judgment with Each Type of Disc 9.6.1 Verification of Disc Judgments 9.6.2 Auto-Adjustments 9.6.3 Tracking Error Level Adjustment and Disc Determination 9.6.4 Recording Power Sweep Mode for Recording Power Calibration | 34 34 34 34 35 35 35 35 36 36 37 37 37 37 37 37 47 40 40 40 41 |

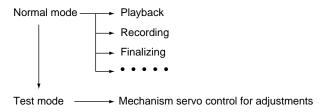

| 10. ABOUT TEST MODE OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41                                                             |

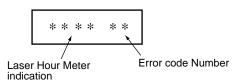

| 11. ERROR CODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45                                                             |

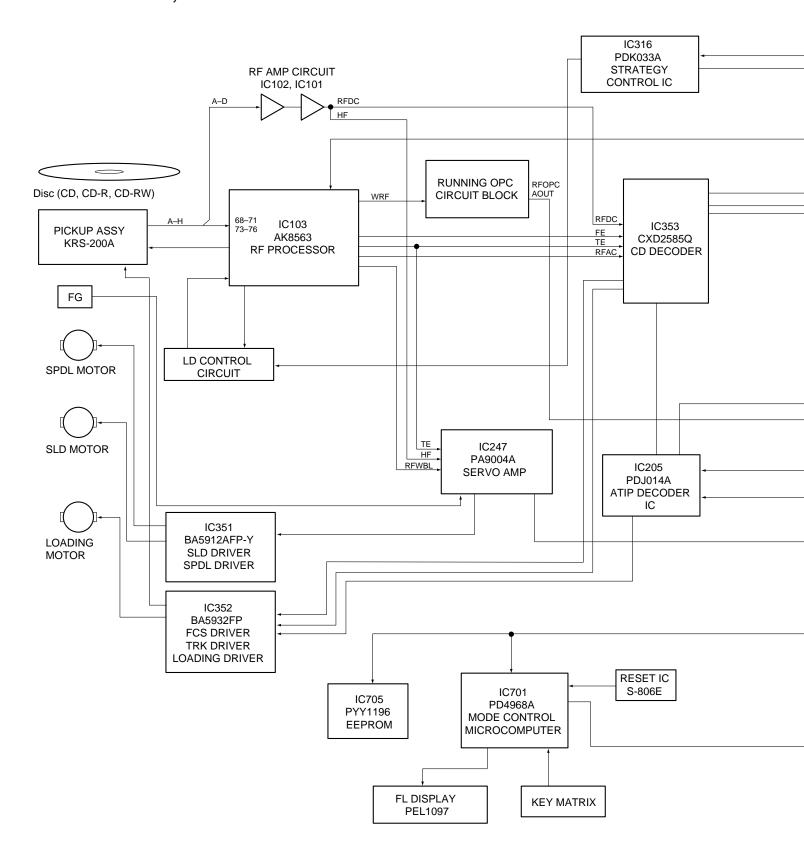

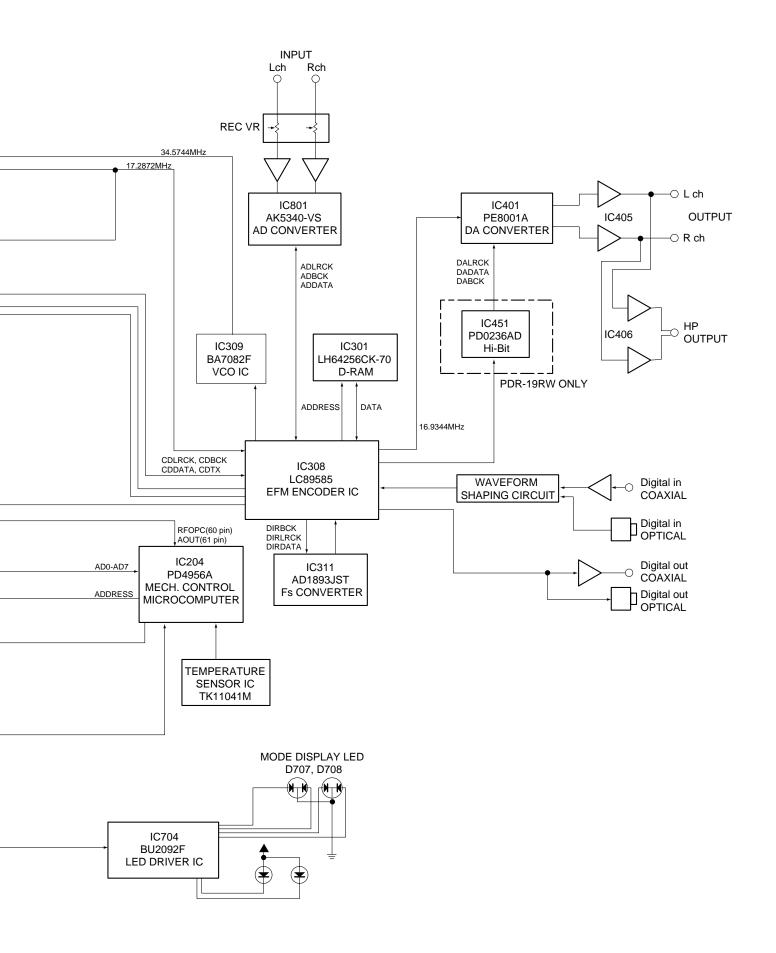

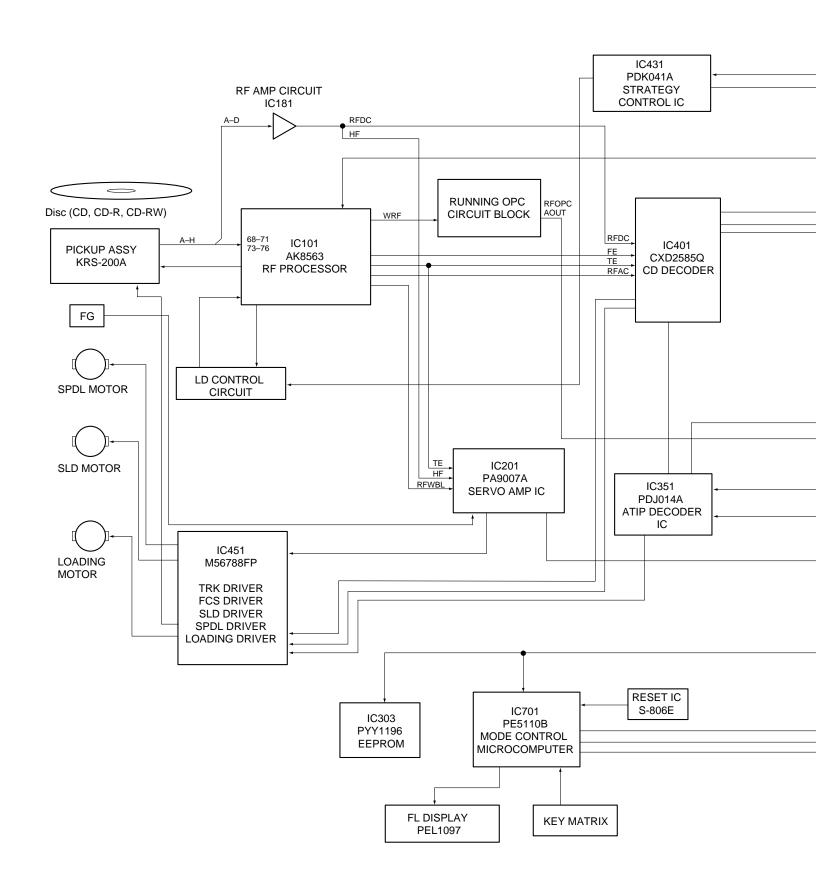

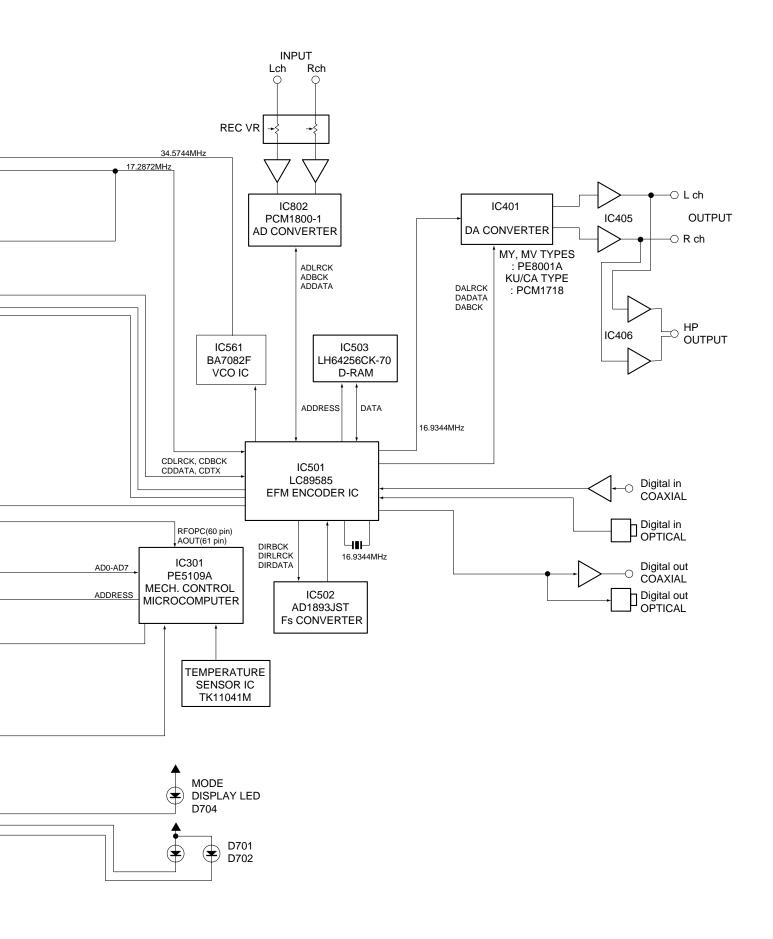

#### 1. BLOCK DIAGRAM

#### 1.1 PDR-555RW, PDR-V500 AND PDR-19RW

#### 1.2 PDR-509

### 2. PRODUCT DESCRIPTIONS

The PDR-555RW series (PDR-555RW, PDR-V500 and PDR-19RW) is the first series of CD recorders from PIONEER that supports recording and erasing of CD-RW discs. Basic operations with CDs and CD-Rs with this series are based on those of the CD recorders of the PDR-05 series.

The main differences from the PDR-05 series concerning the circuits are:

- The pickup is changed.

- The circuit in RF amplifier is changed.

- The LD drive circuit (including the strategy control circuit) is changed.

- A running OPC circuit is added.

- The focus servo, tracking servo and sled servo are digitized.

- The driver IC is changed.

- The CD decoder IC is changed.

- The sampling rate converter IC is changed.

- The DA converter is changed.

Also, the circuits of the CD recorders of the PDR-509 series are based on those of the PDR-555RW series. So the main circuits used in the PDR-509 series are equivalent to those of the PDR-555RW series. But as an exception, AD converter is changed to the AK5340-VS from the PCM1800-1.

## 3. PORT TABLE OF MICROCOMPUTER

• The information shown in the list is basic information and may not correspond exactly to that shown in the schematic diagrams.

## 3.1 MODE CONTROL OF PDR-555RW, PDR-V500 AND PDR-19RW

#### ■ PD4968A (FUNCTION ASSY: IC701)

#### Mode Control IC

| FIPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No. | Mark  | Pin Name | I/O | Pin Function                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------|-----|----------------------------------------------------------------------------------------------|

| FIP5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _   | -     |          |     |                                                                                              |

| FIP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       |          |     |                                                                                              |

| FIP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       |          |     |                                                                                              |

| 5         FIP2         GRID 2         O         FL grid output 9           6         FIP1         GRID 1         O         FL grid output 10           7         FIP0         GRID 0         O         FL grid output 11           8         VDD         -         -         Connect to VDD           9         SCOK         RSCK         O         Serial clock for JIG communication           10         SOO         RSO         O         Serial input for JIG communication           11         SIO         RSI         I         Serial input for JIG communication           12         P24         XTAL         O         XTAL ONOFF (AI digital selection without FS converter: L)           13         P23         XEVCO         O         Encoder VCO ONOFF (AI CD : H)           14         SCK1         FSCK         I/O         Serial clock of the mechanism controller LSI           15         SOI I         FSO         O         Serial clock of the mechanism controller LSI           16         SI I         FSI         I         Serial input of the mechanism controller LSI           17         RESET         XESEST         O         Reset input of the mechanism controller LSI           18         P74 <td< td=""><td></td><td></td><td></td><td></td><td></td></td<>                                                                                         |     |       |          |     |                                                                                              |

| 6         FIP1         GRID 1         O         FL grid output 10           7         FIP0         GRID 0         O         FL grid output 11           8         VDD         -         -         Connect to VDD           9         SCOK         RSCK         O         Serial clock for JIG communication           10         SOO         RSO         O         Serial output for JIG communication           11         SIO         RSI         I         Serial output of JIG communication           12         P24         XTAL         O         XTAL ON/OFF (At digital selection without FS converter : L)           13         P23         XEVCO         O         Encoder VCO ON/OFF (At CD: H)           14         SCK1         FSCK         I/O         Serial clock of the mechanism controller LSI           15         SO1         FSC         O         Serial output of the mechanism controller LSI           16         SI         FSI         I         Serial pout of the mechanism controller LSI           17         RESET         XRSETS         O         Residency input of the mechanism controller LSI           18         P74         LDATA         O         Communication data input for LED driver           19                                                                                                                                           |     |       |          |     |                                                                                              |

| FIPO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       |          |     |                                                                                              |

| VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       | GRID 1   | 0   |                                                                                              |

| SCOK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7   | FIP0  | GRID 0   | 0   | FL grid output 11                                                                            |

| 10   SOO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8   | VDD   | _        | -   | Connect to VDD                                                                               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9   | SCOK  | RSCK     | 0   | Serial clock for JIG communication                                                           |

| 12   P24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10  | SO0   | RSO      | 0   | Serial output for JIG communication                                                          |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11  | SI0   | RSI      | - 1 | Serial input for JIG communication                                                           |

| 14         SCK1         FSCK         I/O         Serial clock of the mechanism controller LSI           15         SO1         FSO         O         Serial output of the mechanism controller LSI           16         SI         FSI         I         Serial input of the mechanism controller LSI           17         RESET         XRESET         O         Reset input of the mode controller           18         P74         LDATA         O         Communication data output for LED driver           19         P73         LCLOCK         O         Communication data input for LED driver           20         AVSS         GND         I         Connect to VDD           21         P17         XFUSE         O         During use the serial communication between the mode controller and LC89585 (During use: L)           22         P16         LCK         O         Communication latch output for LED driver           23         P15         XVCO         O         PLL ON/OFF (For SRC ON/OFF SRC OFF: L)           24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for LED driver           26         P12         XRST         O         Reset output                                                                                                     | 12  | P24   | XTAL     | 0   | XTAL ON/OFF (At digital selection without FS converter : L)                                  |

| 15   SO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13  | P23   | XEVCO    | 0   | Encoder VCO ON/OFF (At CD : H)                                                               |

| FSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14  | SCK1  | FSCK     | I/O | Serial clock of the mechanism controller LSI                                                 |

| 17         RESET         XRESET         O         Reset input of the mode controller           18         P74         LDATA         O         Communication data output for LED driver           19         P73         LCLOCK         O         Communication data input for LED driver           20         AVSS         GND         I         Connect to VDD           21         P17         XFUSE         O         During use the serial communication between the mode controller and LC89585 (During use: L)           22         P16         LCK         O         Communication latch output for LED driver           23         P15         XVCO         O         PLL ON/OFF (For SRC ON/OFF SRC OFF: L)           24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection ( At optical input selection : L)           28         P10         -         O         Not used (A/D input)           30         AVREF         VDD         -                                                                                                    | 15  | SO1   | FSO      | 0   | Serial output of the mechanism controller LSI                                                |

| 18         P74         LDATA         O         Communication data output for LED driver           19         P73         LCLOCK         O         Communication data input for LED driver           20         AVSS         GND         I         Connect to VDD           21         P17         XFUSE         O         During use the serial communication between the mode controller and LC89585 (During use: L)           22         P16         LCK         O         Communication latch output for LED driver           23         P15         XVCO         O         PLL ON/OFF (For SRC ON/OFF SRC OFF: L)           24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection (At optical input selection: L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to GND <td>16</td> <td>SI</td> <td>FSI</td> <td>I</td> <td>Serial input of the mechanism controller LSI</td> | 16  | SI    | FSI      | I   | Serial input of the mechanism controller LSI                                                 |

| P73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17  | RESET | XRESET   | 0   | Reset input of the mode controller                                                           |

| 20         AVSS         GND         I         Connect to VDD           21         P17         XFUSE         O         During use the serial communication between the mode controller and LC89585 (During use : L)           22         P16         LCK         O         Communication latch output for LED driver           23         P15         XVCO         O         PLL ON/OFF (For SRC ON/OFF SRC OFF: L)           24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection ( At optical input selection : L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used                                                                                                                               | 18  | P74   | LDATA    | 0   | Communication data output for LED driver                                                     |

| 21         P17         XFUSE         O         During use the serial communication between the mode controller and LC89585 (During use : L)           22         P16         LCK         O         Communication latch output for LED driver           23         P15         XVCO         O         PLL ON/OFF (For SRC ON/OFF SRC OFF: L)           24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection ( At optical input selection : L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           34         X1         -         I           35         X2 <td>19</td> <td>P73</td> <td>LCLOCK</td> <td>0</td> <td>Communication data input for LED driver</td>                             | 19  | P73   | LCLOCK   | 0   | Communication data input for LED driver                                                      |

| 22         P16         LCK         O         Communication latch output for LED driver           23         P15         XVCO         O         PLL ON/OFF (For SRC ON/OFF SRC OFF: L)           24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection (At optical input selection: L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O <td>20</td> <td>AVSS</td> <td>GND</td> <td>I</td> <td>Connect to VDD</td>                                                                                   | 20  | AVSS  | GND      | I   | Connect to VDD                                                                               |

| P15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21  | P17   | XFUSE    | 0   | During use the serial communication between the mode controller and LC89585 (During use : L) |

| 24         P14         FS_THR         O         SRC through output           25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection (At optical input selection: L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           MODEL_2                                                                                                                                                                                      | 22  | P16   | LCK      | 0   | Communication latch output for LED driver                                                    |

| 25         P13         DACLAT         O         Communication latch output for D/A converter           26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection (At optical input selection: L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         O           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           Model switching pin <td>23</td> <td>P15</td> <td>XVCO</td> <td>0</td> <td>PLL ON/OFF (For SRC ON/OFF SRC OFF: L)</td>                                                                                            | 23  | P15   | XVCO     | 0   | PLL ON/OFF (For SRC ON/OFF SRC OFF: L)                                                       |

| 26         P12         XRST         O         Reset output for mechanism controller and ATIP decoder (H: release the reset)           27         P11         XOPT         O         Optical input selection ( At optical input selection : L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         System oscillation 4.19MHz           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           Model switching pin                                                                                                                                                                                                                                                                          | 24  | P14   | FS_THR   | 0   | SRC through output                                                                           |

| 27         P11         XOPT         O         Optical input selection ( At optical input selection : L)           28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         System oscillation 4.19MHz           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I    Model switching pin                                                                                                                                                                                                                                                                                                                                                                    | 25  | P13   | DACLAT   | 0   | Communication latch output for D/A converter                                                 |

| 28         P10         -         O         Not used (A/D input)           29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         O           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I    Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26  | P12   | XRST     | 0   | Reset output for mechanism controller and ATIP decoder (H: release the reset)                |

| 29         AVDD         VDD         -         Connect to VDD           30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         O           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I         Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27  | P11   | XOPT     | 0   | Optical input selection ( At optical input selection : L)                                    |

| 30         AVREF         VDD         -         Connect to VDD           31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         O           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I         Model switching pin           39         P34         MODEL_2         I         Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28  | P10   | _        | 0   | Not used (A/D input)                                                                         |

| 31         P04         ROT_DI         I         For judgement of the rotary encoder SW direction           32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         System oscillation 4.19MHz           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I    Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29  | AVDD  | VDD      | _   | Connect to VDD                                                                               |

| 32         XT2         -         O         Not used           33         VSS         GND         -         Connect to GND           34         X1         -         I         System oscillation 4.19MHz           35         X2         -         O         Demo mode ON/OFF L: Demo display exist           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           Model switching pin           39         P34         MODEL_2         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30  | AVREF | VDD      | _   | Connect to VDD                                                                               |

| 33         VSS         GND         —         Connect to GND           34         X1         —         I         System oscillation 4.19MHz           35         X2         —         O         O           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I    Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31  | P04   | ROT_DI   | ı   | For judgement of the rotary encoder SW direction                                             |

| 34       X1       -       I       System oscillation 4.19MHz         35       X2       -       O       Demo mode ON/OFF L: Demo display exist         36       P37       SW1       I       Demo mode ON/OFF L: Demo display exist         37       P36       MODEL_0       I         38       P35       MODEL_1       I         39       P34       MODEL_2       I     Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32  | XT2   | _        | 0   | Not used                                                                                     |

| 35         X2         -         O         System oscillation 4.19MHz           36         P37         SW1         I         Demo mode ON/OFF L: Demo display exist           37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I    Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33  | VSS   | GND      | _   | Connect to GND                                                                               |

| 35       X2       -       O       '         36       P37       SW1       I       Demo mode ON/OFF L: Demo display exist         37       P36       MODEL_0       I         38       P35       MODEL_1       I         39       P34       MODEL_2       I     Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34  | X1    | _        | ı   |                                                                                              |

| 37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I   Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35  | X2    | _        | 0   | System oscillation 4.19MHz                                                                   |

| 37         P36         MODEL_0         I           38         P35         MODEL_1         I           39         P34         MODEL_2         I   Model switching pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36  | P37   | SW1      | ı   | Demo mode ON/OFF L: Demo display exist                                                       |

| 38         P35         MODEL_1         I         Model switching pin           39         P34         MODEL_2         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37  | P36   | MODEL_0  | ı   |                                                                                              |

| 39 P34 MODEL_2 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38  | P35   | MODEL_1  | ı   | Model switching pin                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39  | P34   |          | I   |                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40  | P33   |          | 0   | CE output for JIG communication                                                              |

## PDR-555RW, PDR-V500, PDR-19RW, PDR-509

| No. | Mark  | Pin Name | I/O | Pin Function                                            |  |

|-----|-------|----------|-----|---------------------------------------------------------|--|

| 41  | P32   | MACK     | 0   | Communication response for mechanism controller         |  |

| 42  | P31   | LREQ     | 0   | CE signal for LC89585                                   |  |

| 43  | P30   | UNLOCK   | I   | Digital unlock detection                                |  |

| 44  | INTP3 | POT_INT  | I   | Rotary encoder SW operation detection ( ↓ interrupt)    |  |

| 45  | INTP2 | XPFAIL   | I   | Power down detection                                    |  |

| 46  | INTP1 | MREQ     | 1   | Mechanism controller communication request (interrupt)  |  |

| 47  | INTP0 | REMIN    | I   | Remote control input (interrupt)                        |  |

| 48  | IC    | VPP      | ı   | Connect to GND                                          |  |

| 49  | P72   | ISEL3    | ı   | Input selector rotary SW input 3 (H: Analog selection)  |  |

| 50  | P71   | ISEL2    | I   | Input selector rotary SW input 2 (H: Optical selection) |  |

| 51  | P70   | ISEL1    | I   | Input selector rotary SW input 1 (H: Coaxial selection) |  |

| 52  | VDD   | VDD      | _   | Connect to VDD                                          |  |

| 53  | P127  | SCAN4    | 0   | Key matrix output 4                                     |  |

| 54  | P126  | SCAN3    | 0   | Key matrix output 3                                     |  |

| 55  | P125  | SCAN2    | 0   | Key matrix output 2                                     |  |

| 56  | P124  | SCAN1    | 0   | Key matrix output 1                                     |  |

| 57  | P123  | SCAN0    | 0   | Key matrix output 0                                     |  |

| 58  | P122  | KEYIN3   | I   | Key matrix input 3                                      |  |

| 59  | P121  | KEYIN2   | I   | Key matrix input 2                                      |  |

| 60  | P120  | KEYIN1   | I   | Key matrix input 1                                      |  |

| 61  | P117  | KEYIN0   | I   | Key matrix input 0                                      |  |

| 62  | P116  | ATT_0V   | I   |                                                         |  |

| 63  | P115  | AATLAT   | 0   |                                                         |  |

| 64  | P114  | FINL_SEG | 0   | "FINALIZE" segment output (At lights up: H)             |  |

| 65  | P113  | SEG 10   | 0   | FL segment output 10                                    |  |

| 66  | P112  | SEG 9    | 0   | FL segment output 9                                     |  |

| 67  | P111  | SEG 8    | 0   | FL segment output 8                                     |  |

| 68  | P110  | SEG 7    | 0   | FL segment output 7                                     |  |

| 69  | P107  | SEG 6    | 0   | FL segment output 6                                     |  |

| 70  | P106  | SEG 5    | 0   | FL segment output 5                                     |  |

| 71  | VLOAD | VLOAD    | -   | VLOAD                                                   |  |

| 72  | P105  | SEG 4    | 0   | FL segment output 4                                     |  |

| 73  | P104  | SEG 3    | 0   | FL segment output 3                                     |  |

| 74  | P103  | SEG 2    | 0   | FL segment output 2                                     |  |

| 75  | P102  | SEG 1    | 0   | FL segment output 1                                     |  |

| 76  | P101  | SEG 0    | 0   | FL segment output 0                                     |  |

| 77  | P100  | GRID10   | 0   | FL grid output 10                                       |  |

| 78  | FIP9  | GRID 9   | 0   | FL grid output 9                                        |  |

| 79  | FIP8  | GRID 8   | 0   | FL grid output 8                                        |  |

| 80  | FIP7  | GRID 7   | 0   | FL grid output 7                                        |  |

## 3.2 MECHANISM CONTROL OF PDR-555RW, PDR-V500 AND PDR-19RW

### ■ PD4956B (SERVO DIGITAL ASSY : IC204)

#### • Mechanism Control IC

| No. | Mark                 | Pin Name | I/O  | Pin Function                                                    |

|-----|----------------------|----------|------|-----------------------------------------------------------------|

| 1   | P32/XCLK0/SCL        | MSCK     | O(I) | Serial transfer clock output of clock synchronous system        |

| 2   | P33/SO0/SDA          | MSO      | O(I) | Serial transfer data output of clock synchronous system         |

| 3   | P34/TO0              | _        | 0    | Not used                                                        |